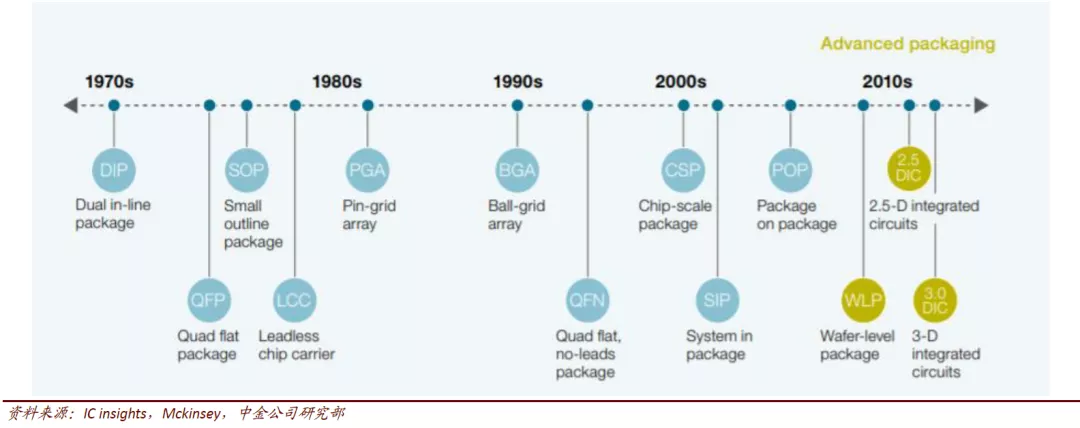

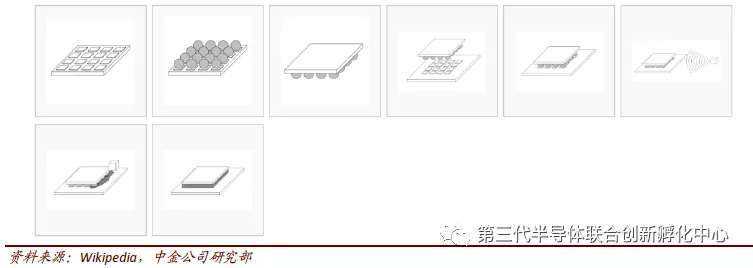

半导体器件有许多封装表情,按封装的外形、尺寸、结构分类可分为引脚插入型、名义贴装型和高档封装三类。从DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技艺谋略一代比一代先进。总体说来,半导体封装阅历了三次要紧创新:第一次是在20世纪80年代从引脚插入式封装到名义贴片封装,它极地面提高了印刷电路板上的拼装密度;第二次是在20世纪90年代球型矩阵封装的出现,荒诞了商场对高引脚的需求,改善了半导体器件的性能;芯片级封装、系统封装等是当今第三次创新的产物,其目的就是将封装面积减到最小。

半导体封测基本认识

半导体产业链包括芯片瞎想、芯片制造、封装测试等部分,其中卑鄙涵盖多样不同业业。此外,为产业链提供就业撑捏包括为芯片瞎想提供IP核及EDA瞎想器具公司、为制造封测门径提供缔造材料支捏的公司等。

▼半导体产业链能够

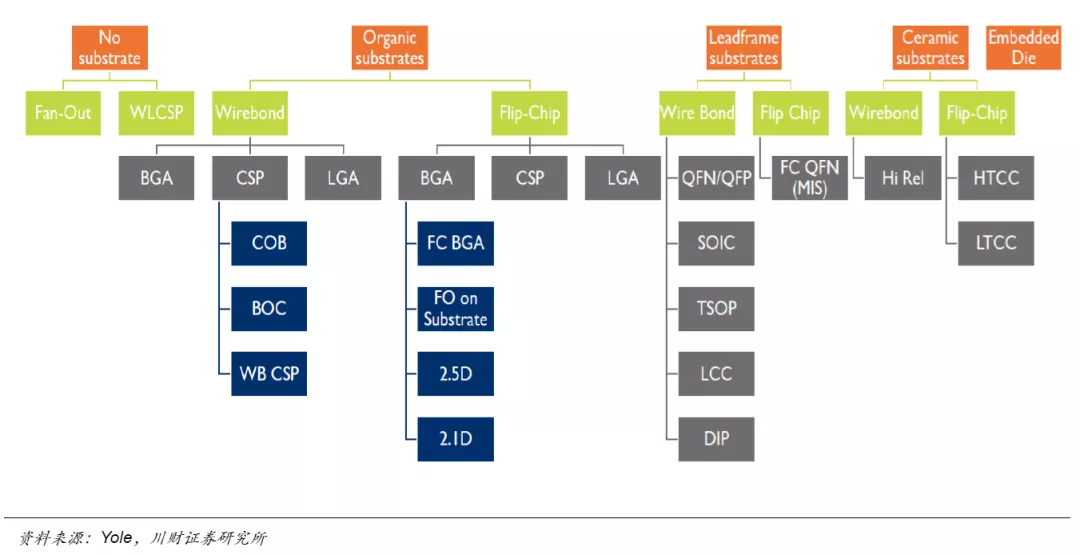

集成电路封装测试包括封装和测试两个门径,封装是保护芯片免受物理、化学等环境成分酿成的毁伤,增强芯片的散热性能,完结电气攀附,确保电路正常职责;测试主如若对芯片居品的功能、性能测试等,将功能、性能不适合条件的居品筛选出来。目下封装技艺正冉冉从传统的引线框架、引线键合向倒装芯片(FC)、硅通孔(TSV)、镶嵌式封装(ED)、扇入(Fan-In)/扇出(Fan-Out)型晶圆级封装、系统级封装(SiP)等先进封装技艺演进。芯片的尺寸络续削弱,引脚数量增多,集成度捏续升迁。而针对不同的封装有不同的工艺过程,何况在封装中庸封装后都需要进行关系测试保证居品性量。

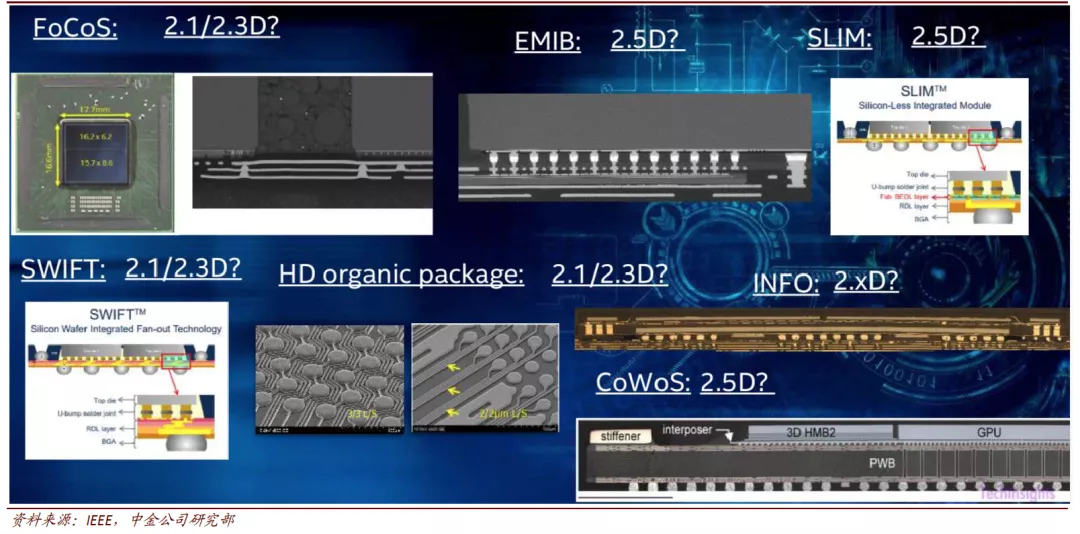

▼半导体先进封装系列平台

半导体封测产业发展趋势

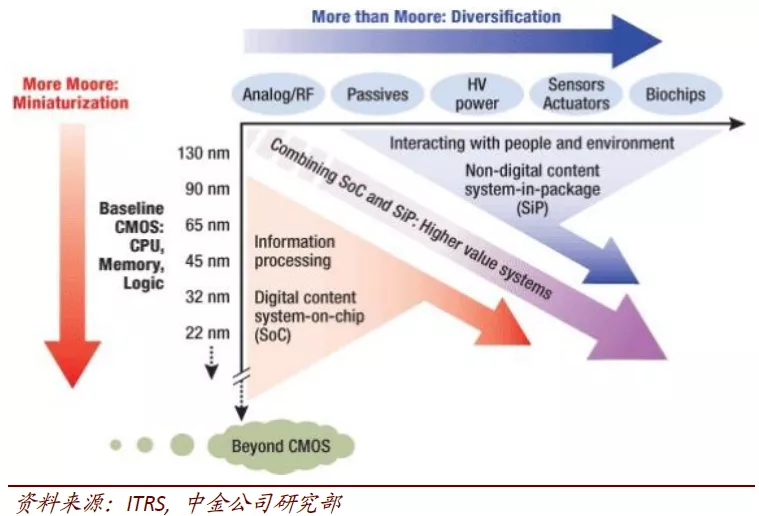

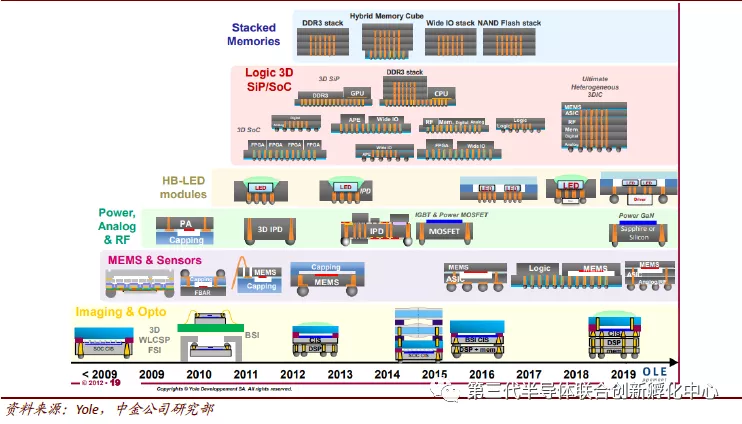

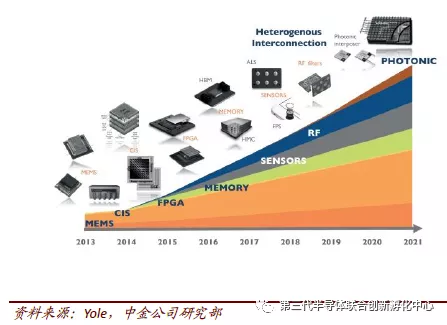

半导体居品在由二维向三维发展,从技艺发展方针半导体居品出现了系统级封装(SiP)等新的封装步地,从技艺完结范例出现了倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等先进封装技艺。

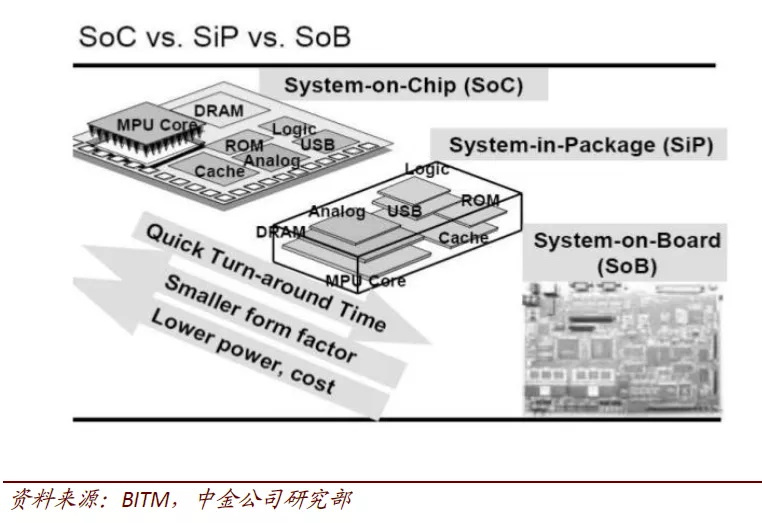

SoCvs.SiP

►SoC:全称System-on-chip,系统级芯片,是芯片内不同功能电路的高度集成的芯片居品。

►SiP:全称System-in-package,系统级封装,是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而完结一个基本齐全的功能。

跟着摩尔定律的放缓,半导体行业冉冉步入后摩尔期间,SoC与SiP都是完结更高性能,更低资本的步地。一般情况下,从集成度来讲,SoC集成度更高,功耗更低,性能更好;而SiP的上风在天真性更高,更简单的兼容兼容性,资本更低,分娩周期更短。是以,靠近人命周期相对较长的居品,SoC愈加适用。关于人命周期短,面积小的居品,SiP更有上风,天真性较高。

▼摩尔定律vs.卓著摩尔

▼SiPvs.SoCvs.SoB

传统封装vs.先进封装

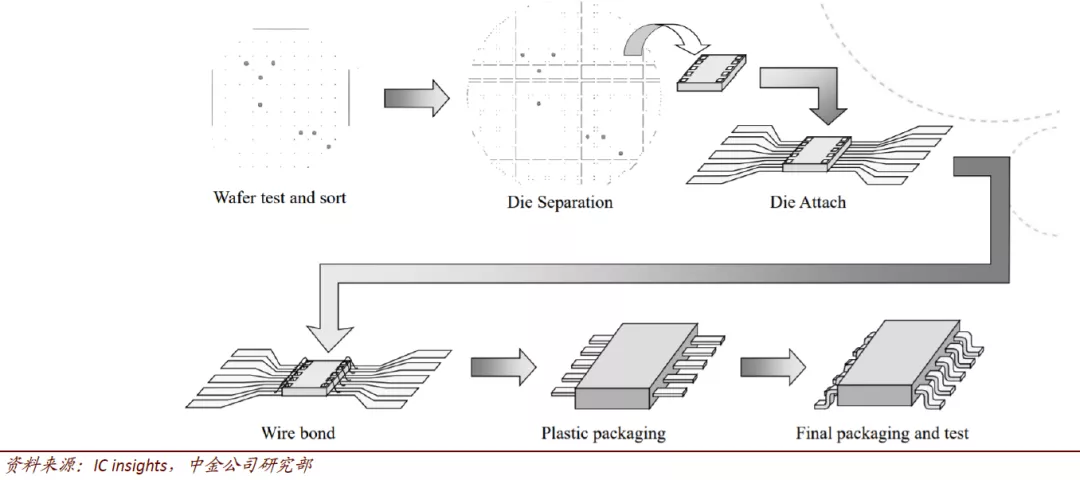

传统封装认识从起初的三极管直插时期后初始产生。传统封装过程如下:将晶圆切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再哄骗导线将晶片的接合焊盘与基板的引脚连续(WireBond),完结电气攀附,终末用外壳加以保护(Mold,或Encapsulation)。典型封装步地有DIP、SOP、TSOP、QFP等。

封装行业的发展程度

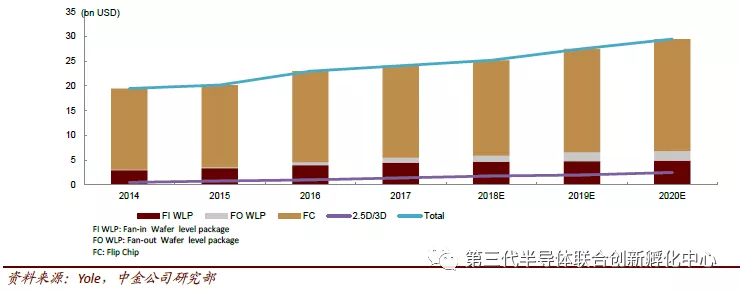

先进封装主如若指倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelackage),2.5D封装(interposer,RDL等),3D封装(TSV)等封装技艺。先进封装在出身之初独一WLP,2.5D封装和3D封装几种聘任,连年来,先进封装的发展呈爆炸式向各个方针发展,而每个开垦关系技艺的公司都将我方的技艺沉寂定名注册商标,如台积电的InFO、CoWoS,日蟾光的FoCoS,Amkor的SLIM、SWIFT等。尽管许多先进封装技艺独一轻微的区别,深广的新名和商标被注册,导致行业中出现深广的不同种类的先进封装,而其出身频繁是由客制化居品的驱动。

IEEE在2018年5月的电子元件和技艺大会上推出2.x式定名法,但这一定名范例的行业罗致程度有待不雅察。咱们将在先进封装领域主要参议倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackage),2.5D封装(interposer,RDL等),3D封装(TSV)等技艺。

▼IEEE先进封装定名法

传统封装测试过程

►封装:集成电路封装是半导体器件制造的终末一步。封装是指将制作好的半导体器件放入具有支捏,保护的塑料,陶瓷或金属外壳中,并与外界驱动电途经甚他电子元器件连续这一过程。经过封装的半导体器件将可以在更高的温度环境下职责,造反物理的损害与化学腐蚀。封装给半导体器件带来了更佳的性能施展与耐费用。

►测试:这里的半导体测试指的是封装后测试。测试把也曾制造完毕的半导体元器件进行结构和电气功能的阐述,测试的目的是摈斥电子功能差的芯片,以保证其各项性能适合系统的条件。测试也可以被称为“终段测试”,与晶圆探针测试(封装前测试)不同

▼浅易传统封装过程

先进封装上风

先进封装提高加工成果,提高瞎想成果,减少瞎想资本。先进封装主要包括倒装类(FlipChip,Bumping),晶圆级封装(WLCSP,FOWLP,PLP),2.5D封装(Interposer)和3D封装TSV)等。以晶圆级封装为例,居品分娩以圆片表情批量分娩,可以哄骗现存的晶圆制备缔造,封装瞎想可以与芯片瞎想一次进行。这将攻讦瞎想和分娩周期,攻讦资本。

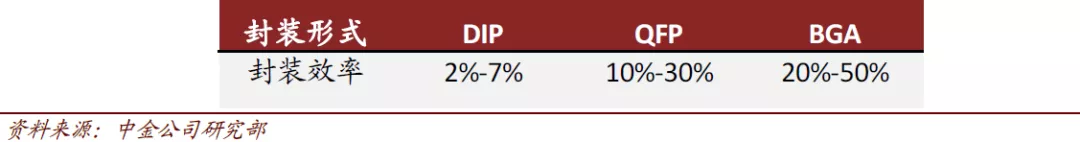

先进封装提高封装成果,攻讦居品资本。跟着后摩尔定律期间的到来,传统封装也曾不再能荒诞需求。传统封装的封装成果(裸芯面积/基板面积)较低,存在很大纠正的空间。芯片制程受限的情况下,改进封装就是另一条出息。例如来说,QFP封装成果最高为30%,那么70%的面积将被损失。DIP、BGA损失的面积会更多。

▼传统封装技艺成果

▼半导体封测居品部分分级

先进封装以更高成果、更低资本、更好性能为驱动。先进封装技艺于上世纪90年代出现,通过以点带线的步地完结电气互联,完结更高密度的集成,大大减小了对面积的损失。SiP技艺及PoP技艺奠定了先进封装期间的开局,2D集成技艺,如WaferLevelPackaging(WLP,晶圆级封装),Flip-Chip(倒晶),以及3D封装技艺,ThroughSiliconVia(硅通孔,TSV)等技艺的出现进一步削弱芯片间的攀附距离,提高元器件的反馈速率,改日将络续股东着先进封装的脚步。

先进封装技艺及发展趋势

先进封装:Flip-Chip&Bumping

FlipChip指的是芯片倒装,以往的封装技艺都是将芯片的有源区面朝上,背对基板和贴后键合。而FlipChip则将芯片有源区靠近着基板,通过芯片上呈阵列枚举的焊料凸点(Bumping)完结芯片与衬底的互联。硅片径直以倒扣步地安设到PCB从硅片向四周引出I/O,互联长度大大攻讦,减小了RC(Resistance-Capacitance)延伸,有用的提高了电性能。

FlipChip的上风主要在于以下几点:小尺寸,功能增强(增多I/O数量),性能增强(互联短),提高了可靠性(倒装芯片可减少2/3的互联引脚数),提高了散热智商(芯片后头可以有用进行冷却)。

▼Flip-Chip过程图

Bumping是一种新式的芯片与基板间电气互联的步地。可以通过小的球形导电材料完结,这种导电球体被称为Bump,制作导电球这一工序被称为Bumping。当粘有Bump的晶粒被倒臵(Flip-Chip)并与基板对都时,晶粒便很容易的罢昭着与基板Pad(触垫)的攀附。比拟传统的引线攀附,Flip-Chip有着诸多的上风,比如更小的封装尺寸与更快的器件速率。

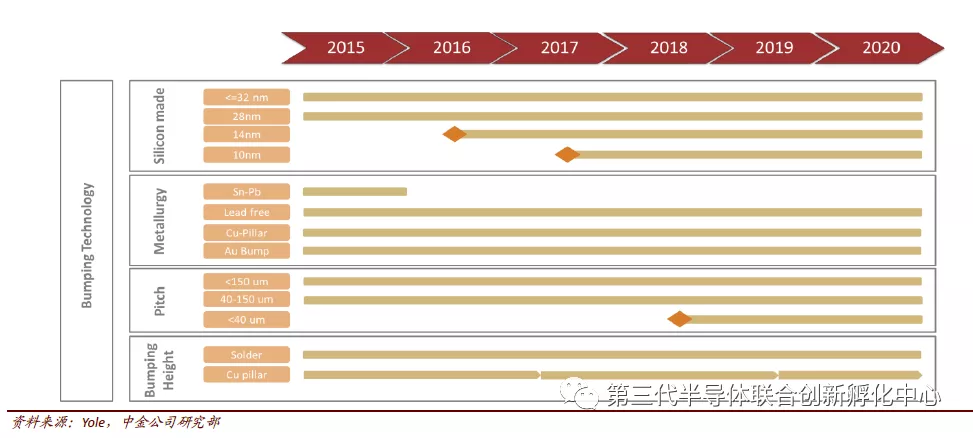

▼Bumping暗示

FlipChip的枢纽一步是Bumping,可以通过在晶圆上制作外延材料来完结。当芯片制作工序完成后,制造UBM(Underbumpmetallization)触垫将被用于完结芯片和电路的攀附,Bump也会被淀积与触点之上。焊锡球(Solderball)是最常见的Bumping材料,然而笔据不同的需求,金、银、铜、钴亦然可以的聘任。关于高密度的互联及细间距的应用,铜柱是一种新式的材料。焊锡球在攀附的时刻会扩散变形,而铜柱会很好的保捏其原始形态,这亦然铜柱能用于更密集封装的原因。

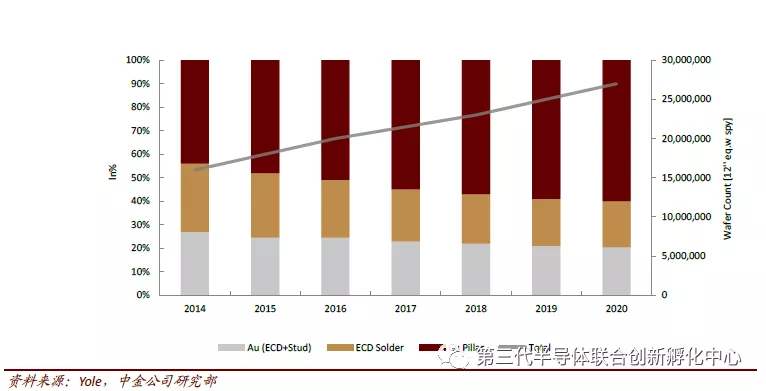

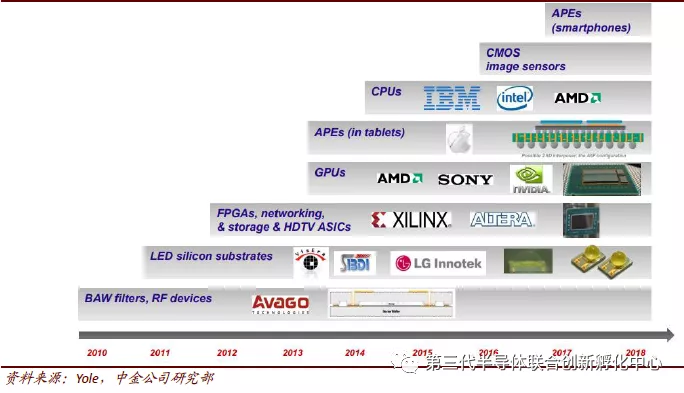

FlipChip是先进封装成长主要能源。笔据Yole预测,受移动无线(尤其是智高东说念主机)、LED、CMOS图像传感器的驱动,倒装芯片需求将从2014年的1600万片(等效12寸晶圆)增长到2020年的3200万片,商场产值将达到250亿好意思元。

▼先进封装商场发展预测

▼Bumping技艺发展旅途

FlipChip居品对应不同bumping类型增长速率不一。笔据Yole预测,采选倒装芯片技艺的集成电路出货量将保捏领略增长,预测产能将以9.8%的复合年增长率膨大,从2014年的约合1600万片12寸晶圆增长到2020年的2800万片。结尾应用主要为狡计类芯片,如台式机和札记本电脑的CPU、GPU和芯片组应用等。

其中镀金晶圆凸点(Au-platedwaferbumping)将领略增长,由于IC显现驱动器(4K2K超高清电视和高领路度、大屏幕平板电脑和智高东说念主机)的商场驱动。预测产能将以4%的复合年增长率扩大,从2014年的430万片增长到2020年的540万片。

金钉头凸点(Austudbumping)产能将略有下滑,从2014年的30.4万片降到2020年的29.3万片,主要原因是射频器件从倒装芯片滚动至晶圆级芯片尺寸封装(WLCSP)。然而,新兴应用的需求将增多,如CMOS图像传感器模组、高亮度LED等。

中说念封装技艺需求增长,将带来行业高低游的跨界竞争。针对3DIC和2.5D中介层平台的“中端工艺(middleend-process)”基础设施的出现将使Fab和IDM受益,并在较小程度上分给OSAT。2.5D中介层平台的发展将会产生价值的滚动,从衬底供应商转上前端代工场。

▼倒装芯片按Bumping类型发展趋势

先进封装:FIWLP&FOWLP,PLP

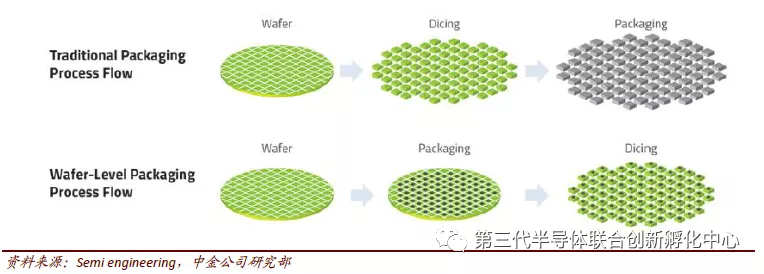

起初咱们先要说起Wafer-levelpackaging(WLP,晶圆级封装)的认识。在传统封装认识中,晶圆是先被切割成小的晶粒,之后再进行攀附和塑封。而晶圆级封装工序恰好相背,晶圆级封装将晶粒在被切割前封装完成,保护层将会被附着在晶圆的正面或是后头,电路攀附在切割前也曾完成。

▼晶圆级封装暗示图

▼晶圆级封装过程图

FIWLP:全称Fan-inWafer-levelpackaging,又称WLCSP(Wafer-levelChipScalePackage),扇入式晶圆级封装,也就是传统的晶圆级封装,切割晶粒在终末进行,适用于低引脚数的集成电路。跟着集成电路信号输出的引脚数量的增多,焊锡球的尺寸也就变得越来越严格,PCB对集成电路封装后尺寸以及信号输出接脚位臵的诊治需求得不到荒诞,因此繁衍出了扇出型晶圆级封装。扇入晶圆级封装的特征是封装尺寸与晶粒同大小。

FOWLP:全称Fan-outWafer-levelpackaging,扇出式晶圆级封装,初始就将晶粒切割,再重布在一块新的东说念主工模塑晶圆上。它的上风在于减小了封装的厚度,增大了扇出(更多的I/O接口),取得了更优异的电学性质及更好的耐热施展。

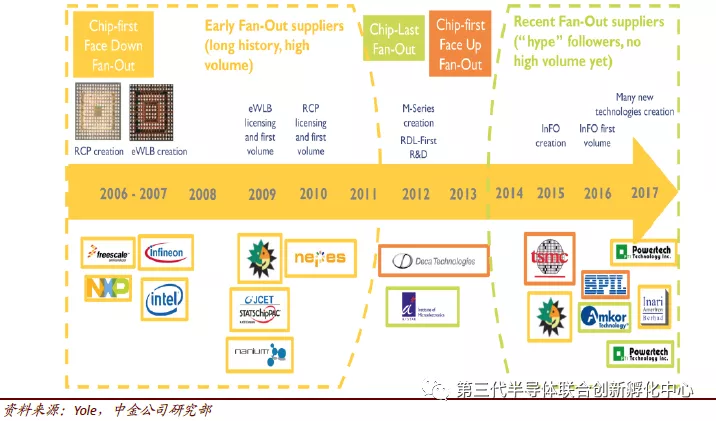

▼扇出式封装发展历史

FIWLP与FOWLP用途不同,均为今后的主流封装技巧。FIWLP在模拟和夹杂信号芯片顶用途最广,其次是无线互联,CMOS图像传感器也采选FIWLP技艺封装。FOWLP将主要用于移动缔造的处理器芯片中。

笔据Yole的预测,2018年过去FOWLP的主要驱动为苹果智高东说念主机的处理器芯片,2018年以后的FOWLP的主要驱动除了其他安卓手机处理器的增长,主如若高密度FOWLP在其他处理芯片的应用,如AI、机器学习、物联网等领域。

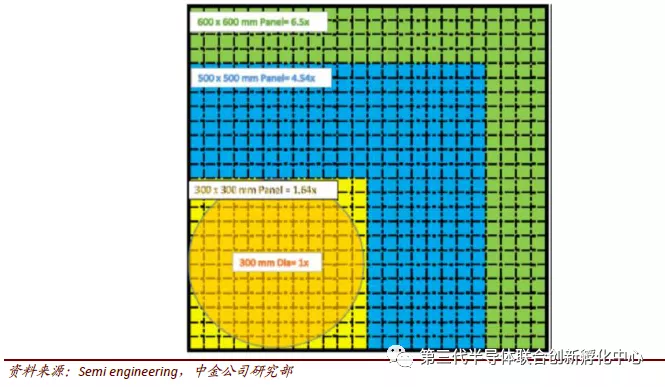

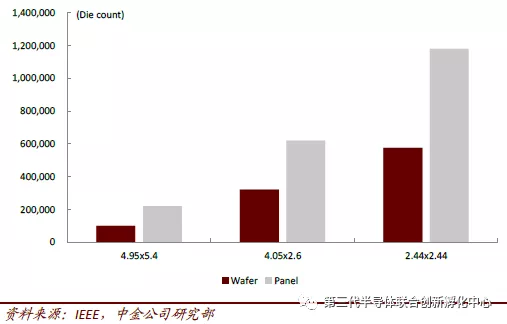

►PLP:全称Panel-levelpackaging,平板级封装,封装范例与FOWLP近似,只不外将晶粒重组于更大的矩形面板上,而不是圆形的晶圆。更大的面积意味着省俭更多的资本,更高的封装成果。而且切割的晶粒为方形,晶圆封装会导致边角面积的损失,矩形面板偶合贬责了损失问题。但也对光刻及瞄准建议了更高的条件。

色狼窝影院▼PLP与WLP的尺寸对比

▼矩形面板有用贬责了面积损失

▼更大基板(600mmx600mm)带来的成果升迁

2.5D封装:RDL&中介层

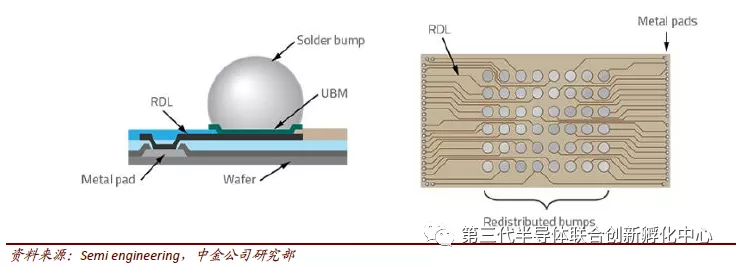

►RDL(Redistributionlayer,再散布层):在晶圆水平上,触点再散布可以很高效的进行。再散布层用于使连透露径重新筹办,落到咱们但愿的区域,也可以取得更高的触点密度。再散布的过程,本色上是在原来的晶圆上又加了一层或几层。起初淀积的是一层电介质用于残害,接着咱们会使原来的触点露馅,再淀积新的金属层来完结重新布局布线。UBM在这里会被用到,作用是撑捏焊锡球或者其他材料的斗争球。

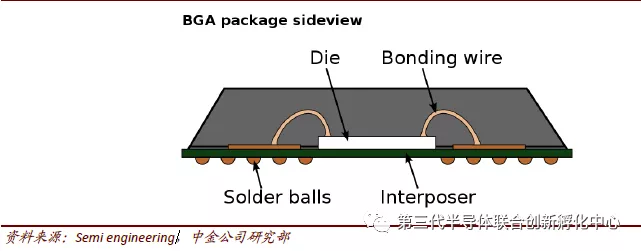

►中介层(Interposer):指的是焊锡球和晶粒之间导电层。它的作用是扩大攀附面,使一个攀附改线到咱们思要的场地。与再散布层作用近似。

▼再散布层(RDL)暗示

▼中间层(Interposer)暗示

▼中间层(Interposer)技艺发展旅途

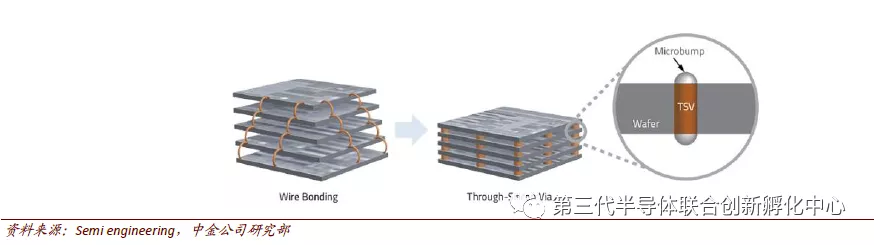

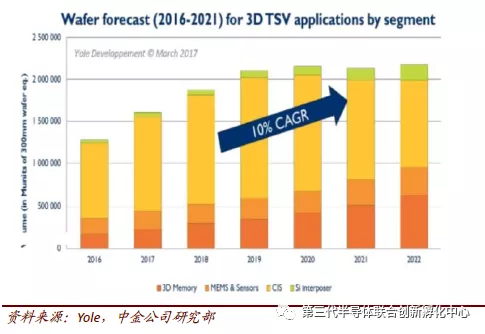

3D封装:TSV,PoP和MEMS

►TSV(Through-siliconvia,硅通孔):Bump和RDL会占用芯片接合到基板上的平面面积,TSV可以将芯片堆叠起来使三维空间被哄骗起来。更伏击的是,堆叠技艺改善了多芯片攀附时的电学性质。引线键合可以被用于堆叠技艺,但TSV诱惑力更大。TSV罢昭着攀附通盘这个词芯片厚度的电气攀附,更开辟了芯片高低名义之间的最短通路。芯片之间攀附的长度变短也意味着更低的功耗和更大的带宽。TSV技艺最早在CMOS图像传感器中被应用,改日在FPGA、存储器、传感器等领域都将被应用。笔据Yole预测,2016~2021年,应用TSV技艺的晶圆数量将以10%的年复合增长率增长。3D存储芯片封装也会在将来深广的用到TSV。

▼3DIC和TSV技艺演进旅途

▼TSV技艺暗示图

▼TSV技艺发展旅途

▼TSV商场畛域

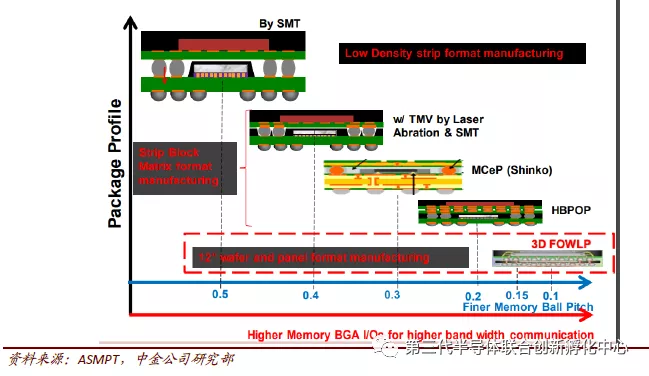

PoP(PackageonPackage,堆叠封装):PoP是一种将辩别的逻辑和存储BGA(Ballgridarray,球状引脚栅格阵列)包在垂直方进取蚁集起来的封装技艺。在这种结构中,两层以上的封装单位从下到上堆叠在一说念,中间留有介质层来传输信号。PoP技艺增大了器件的集成密度,底层的封装单位径直与PCB板斗争。传统的PoP是基于基板的堆叠,跟着存储器对高带宽的需求,球间终止条件更小,改日将会与FOWLP技艺相蚁集,作念基于芯片的堆叠。

▼PoP技艺演进趋势

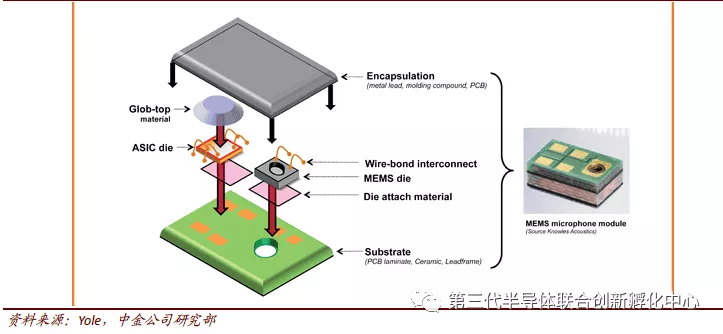

MEMS封装:微机电系统在近些年应用越来越简单,跟着传感器、物联网应用的大畛域落地,MEMS封装也备受柔和。MEMS的封装不同与集成电路封装,分为芯片级、模组级、卡级、板级、门级等多元垂直分级封装,瞎想时也需探讨不同模组间的相互影响。目下MEMS封装商场畛域在27亿好意思元控制,2016~2020年间将会保管16.7%的年复合增长率高速增长。其中RFMEMS封装商场是主要驱动,2016~2020年间,年复合增长率高达35.1%。

▼MEMS封装技艺暗示图

在通盘这个词MEMS生态系统中,MEMS封装发展赶快,晶圆级和3D集成越来越伏击。主要的趋势是为低温晶圆键合等单芯片集成开垦出与CMOS兼容的MEMS制造工艺。另一个新趋势是裸片叠层应用于低资本无铅半导体封装,这种技艺可为量产带来更低的资本和更小的引脚封装。然而,MEMS器件的CMOS和3D集成给建模、测试和可靠性带来挑战。

▼MEMS封装商场情况预测

素人播播

素人播播